MICHALIS KOKOLOGIANNAKIS, National Technical University of Athens, Greece ORI LAHAV, Tel Aviv University, Israel KONSTANTINOS SAGONAS, Uppsala University, Sweden VIKTOR VAFEIADIS, Max Planck Institute for Software Systems (MPI-SWS), Germany

We present a stateless model checking algorithm for verifying concurrent programs running under RC11, a repaired version of the C/C++11 memory model without dependency cycles. Unlike most previous approaches, which enumerate thread interleavings up to some partial order reduction improvements, our approach works directly on execution graphs and (in the absence of RMW instructions and SC atomics) avoids redundant exploration by construction. We have implemented a model checker, called RCMC, based on this approach and applied it to a number of challenging concurrent programs. Our experiments confirm that RCMC is significantly faster, scales better than other model checking tools, and is also more resilient to small changes in the benchmarks.

CCS Concepts: • Theory of computation  $\rightarrow$  Verification by model checking; Program semantics; • Software and its engineering  $\rightarrow$  Software testing and debugging; Concurrent programming languages;

Additional Key Words and Phrases: Software model checking, weak memory models, C/C++11, RC11

#### **ACM Reference Format:**

Michalis Kokologiannakis, Ori Lahav, Konstantinos Sagonas, and Viktor Vafeiadis. 2018. Effective Stateless Model Checking for C/C++ Concurrency. *Proc. ACM Program. Lang.* 2, POPL, Article 17 (January 2018), 32 pages. https://doi.org/10.1145/3158105

# **1 INTRODUCTION**

Suppose we want to verify that a given *multithreaded* program satisfies a given safety specification (e.g., that it never crashes). A standard approach to employ is (bounded) *model checking* [Clarke et al. 1983, 2004; Queille and Sifakis 1982]: explore the set of program states that are reachable from the initial state and determine whether it includes any 'bad' state (i.e., one violating the program's specification). To avoid exploring the same state over and over again, one may straightforwardly just record the set of already visited states. Doing so, however, is often impractical because of the memory required to record this set. This led to *stateless model checking* [Godefroid 1997], which aims to visit all the reachable program states without actually recording them.

Stateless model checking performed naively does not scale because concurrent programs typically have too many interleavings, many of which lead to the same state. This led to techniques, such as *dynamic partial-order reduction* (DPOR) [Flanagan and Godefroid 2005], that cut down some of the redundant explorations.<sup>1</sup> Along this line of work, Abdulla et al. [2014, 2017] have developed

<sup>1</sup>Other competing techniques to DPOR, e.g., MCR [Huang 2015] or techniques based on unfoldings, are discussed in §8. These techniques can in principle explore much fewer states than DPOR, but often yield worse results in practice.

Authors' addresses: Michalis Kokologiannakis, National Technical University of Athens, Greece, michaliskok@softlab. ntua.gr; Ori Lahav, Tel Aviv University, Israel, orilahav@tau.ac.il; Konstantinos Sagonas, Uppsala University, Sweden, kostis@it.uu.se; Viktor Vafeiadis, Max Planck Institute for Software Systems (MPI-SWS), Germany, viktor@mpi-sws.org.

#

This work is licensed under a Creative Commons Attribution 4.0 International License.

© 2018 Copyright held by the owner/author(s). 2475-1421/2018/1-ART17 https://doi.org/10.1145/3158105 an "optimal" DPOR technique for interleaving concurrency in the sense that their algorithm never visits two interleavings that are equivalent up to the reordering of independent transitions.

17:2

Recently, the DPOR approach was extended to the more realistic settings of *weak memory consistency*, which allow more program behaviors than can be captured by the interleaving semantics with the standard memory representation (as a function from locations to values)—a model commonly called sequential consistency (SC) [Lamport 1979]. In particular, DPOR was extended to the TSO and PSO memory models by Abdulla et al. [2015] and Zhang et al. [2015], but in ways that are still very much based on interleaving semantics. This goes against the definition style of many memory models, such as the C/C++ one [Batty et al. 2011], which is *declarative* (a.k.a. axiomatic). In a declarative semantics, program executions are not represented as traces of interleaved actions but rather as partially ordered graphs, which have to satisfy several consistency constraints. With such a semantics, considering thread interleavings is not only unnecessary, but also harmful for scalability. In fact, as Alglave et al. [2013a] point out, model checking for declarative weak memory models may actually be faster than for SC! Intuitively, this stems from the fact that weak memory declarative semantics tend to be based on local conditions whose violations can be efficiently detected, while SC can only be formulated as a global condition on the whole program execution.

In this paper, we suggest a novel approach for stateless model checking for weak memory concurrency, and apply it to RC11—the repaired version of the C/C++ memory model by Lahav et al. [2017], which corrects a number of problems in the original C/C++ model of Batty et al. [2011]. This allows us to reason about program correctness at the programming language level, and also get correctness at the assembly level via the verified compilation schemes from RC11 to x86, ARM, and POWER. Instead of having the algorithm consider the set of all thread interleavings suitably extended with some reorderings, etc., to account for weak memory behaviors, and then quotient that set by some equivalence relation to avoid redundant explorations, we propose something much simpler: to just *enumerate all consistent execution graphs of a program*.

The main challenge is how to generate all consistent execution graphs of a program without (1) generating any inconsistent graphs, (2) generating the same graph multiple times, and (3) storing the set of graphs already generated. The first two constraints are crucial for performance: in particular, the number of execution graphs of a program is typically much larger than the number of its consistent executions.<sup>2</sup> The third constraint is to avoid excessive memory usage.

The key observation that allows us to only consider consistent graphs is that consistency in RC11—as in most other memory models but not in the Batty et al. [2011] model—is *prefix-closed*. Namely, there exists a partial order *R* that includes reads-from and (preserved) program order, such that if an execution graph is consistent, then so is every *R*-prefix of it.<sup>3</sup> Consequently, to generate all consistent graphs, it suffices to start with the initial (empty) graph and extend it gradually by adding one event at a time (in every possible way) and checking for consistency at each step. Since the order in which events are added to a graph is unimportant, to avoid redundant exploration, we fix a certain order (e.g., adding the events of the first thread before those of the second, etc.). This, however, creates another problem, because when a read event is added to the graph, one cannot ensure that all the writes that the read can read from have already been added to the graph.

Accordingly, the second key idea in our algorithm is to extend execution graphs with *revisit sets* capturing the subset of reads whose incoming read-from edges may be changed when a write is added to a graph. When a read is added, the algorithm considers reading from any relevant writes of the existing graph initiating recursive calls to the exploration procedure, and marking the read

Proceedings of the ACM on Programming Languages, Vol. 2, No. POPL, Article 17. Publication date: January 2018.

<sup>&</sup>lt;sup>2</sup>This limits the scalability of research tools, such as herd [Alglave et al. 2014], that enumerate all execution graphs of a suitably restricted program and filter out those that are inconsistent.

<sup>&</sup>lt;sup>3</sup>Batty et al. [2011] allow cycles in program order and reads-from. This results in a number of problems, most importantly the presence of "out-of-thin-air" behaviors [Batty et al. 2015; Boehm and Demsky 2014; Vafeiadis et al. 2015].

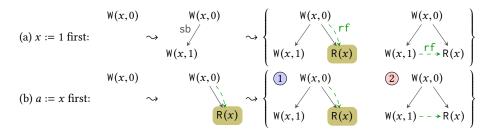

Fig. 1. Two ways of exploring the possible executions of W+R.

as revisitable in exactly one of these calls. Conversely, when a write is added, the algorithm also considers the case where any of the reads in the revisit set could instead read from the new write. A core part of our algorithm concerns the maintenance of the revisit sets in a way that avoids duplication when revisiting existing reads.

Our algorithm handles all the different modes provided by RC11—non-atomics, relaxed, release, acquire, SC—both for accesses and fences. Besides soundness and completeness of our algorithm (i.e., that the algorithm reports a program to be erroneous if and only if the program has some consistent erroneous execution up to some loop unrolling bound), we also prove that our algorithm is *optimal* in the absence of read-modify-write (RMW) accesses and SC atomics. More precisely, we prove that no two sub-explorations of a given RMW-free program could ever visit the same execution; and all explorations of programs without SC atomics result in visiting some RC11-consistent execution of the program.

We have implemented our algorithm in a tool, called RCMC, and applied it to a number of challenging concurrent benchmarks. In §7, we compare our technique with other state-of-the-art stateless model checkers both for SC and weak memory models. The results show that RCMC generally yields lower verification times and scales much better to larger programs. In addition, in comparison to the other tools, RCMC seems to depend much less on the order of threads and on modes of memory accesses. We note that even when RCMC is not optimal (for programs with RMW or SC atomics), our experimental evaluation shows that RCMC runs faster and scales better than other tools.

*Outline.* The remainder of the paper is structured as follows. In §2, we start with the informal overview of our algorithm with examples. We then review the definition of RC11 from Lahav et al. [2017] (§3), present our model checking algorithm and establish its correctness and optimality properties (§4), and outline a possible simplification of the algorithm for a weakened model (§5). We next briefly present our implementations (§6), evaluate the algorithm's performance (§7), discuss related work (§8), and conclude with some possible future work. The supplementary material for this paper, available at http://plv.mpi-sws.org/rcmc/, contain proofs for all claims in the paper, as well as our implementation.

#### 2 OVERVIEW OF OUR APPROACH

We start by explaining our approach by a sequence of small examples. In all of these examples, x, y, z are global variables, while a, b, c, ... are thread-local variables; all global variables are assumed to be zero-initialized by an implicit *main* thread before the other threads are spawned. Unless mentioned otherwise, we assume all of the global variable accesses correspond to RC11 "relaxed" atomic accesses. (Other access modes will be considered in §2.5.)

Fig. 2. Additional exploration steps for coww+R beyond those for w+R.

# 2.1 Constructing Execution Graphs and Marking Nodes Revisitable

Our first example is the following tiny program, which has two RC11-consistent executions.

$$x := 1 || a := x \tag{W+R}$$

The algorithm starts with the initial execution graph containing just the initialization write to x (see Fig. 1(a)). It then adds the x := 1 write, which results in an execution graph with two events. The edge between these two events represents their program order: x := 1 occurs after the (implicit) initialization write of x. Following RC11, we call such edges sb (sequenced before) edges.

Next, the read of x in the second thread is added. At the moment, there are two possible values it can read (0 and 1) because there are two writes to x in the execution graph. Thus, in the third step, the algorithm generates two graphs to be further explored: one for each case. In the execution graphs, we do not actually record the value returned by the read, because that can be deduced from the write event from whence the read reads, which is displayed as being connected with a dashed "reads-from" edge (rf). In one of the two generated graphs, the newly added read node is highlighted, which means that it may be *revisited* in the future if other writes to x are added, and, as a consequence, its read-from edge may be changed. To avoid redundant revisits, we mark the read as revisitable in *only one* of the generated executions.

To understand the use of the revisitable nodes, consider an alternative run of the algorithm that first adds the read of x, as shown in Fig. 1(b). At this point, the only write that the read could read from is the initialization write. As before, the read is marked as revisitable. When, in the next step, the x := 1 write is added, two executions are generated: 1 where the read continues to read from the initialization write, and 2 where it instead reads from the newly added write. In execution 2, we mark the read as no longer revisitable, again to avoid redundant revisits if another write were to be added to the graph. Note that these two executions are identical to the ones generated by adding the events in the other order. Indeed, crucially, unlike naive operational traces, execution graphs do not expose their generation order.

To understand why the read node is left unmarked in execution (2), consider we extend the program by adding another write at the end of the first thread as follows.

$$\begin{array}{c|c} x \coloneqq 1; \\ x \coloneqq 2 \end{array} \quad a \coloneqq x \tag{COWW+R}$$

Further suppose that the x := 1 and a := x have been added yielding the two graphs, (1) and (2), shown already. Next, the x := 2 is to be added. Let's consider the two executions separately. For execution (1), adding the write node generates two graphs (see Fig. 2): (3) where the read continues to read from the initial write and remains revisitable, and (4) where the read is revisited to read from the W(x, 2) event. For (2), as the read of x is not revisitable, only one execution graph is generated ((5)). If the read of (2) were also marked as revisitable, adding the x := 2 write to it would also have generated graph (4), leading to redundant exploration as this graph was also generated from (1).

17:4

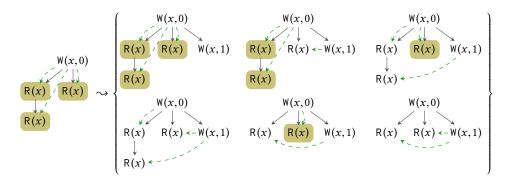

Fig. 3. Key step during the exploration of the possible executions of CO2RRW.

#### 2.2 Revisiting Multiple Reads

We move on to a slightly more advanced example containing multiple reads that need to be revisited when a new write comes along. The following program has six RC11-consistent executions.

$$\begin{array}{c|c} a := x; \\ b := x \end{array} \quad c := x \quad x := 1 \end{array}$$

(CO2RRW)

In the first thread, a = b = 0 or  $a = 0 \land b = 1$  or a = b = 1, while in the second thread, c = 0 or c = 1. (The outcome  $a = 1 \land b = 0$  is forbidden by the "coherence" property of RC11; intuitively, once the first thread has observed the write of x, it cannot later ignore that write and read from an earlier write of x.) After adding the reads, we reach a configuration where all three reads are revisitable and read from the initialization write (see Fig. 3).

Adding the x := 1 write generates six graphs to further explore, also shown in Fig. 3. For every "independent" set of revisitable reads of x, we consider the case where all the reads in the set read from the new write. By independent set, we mean that the set does not contain any nodes that can reach one another. In this case, there are six independent sets—namely,  $\emptyset$ ,  $\{c\}$ ,  $\{b\}$ ,  $\{b,c\}$ ,  $\{a\}$ ,  $\{a,c\}$ —which give rise to the six graphs. Generally, whenever an event is revisited, we remove all of its (sb U rf)-successors from the graph, because reading from a different write may change the value returned by the read and/or the writes the thread has seen, thereby possibly altering the thread-wise execution of the program after that read. Moreover, to avoid redundant explorations, in each execution we mark the revisited reads and all their predecessors as no longer revisitable.

Finally, the two executions whose a := x read was revisited are extended with a read event corresponding to the b := x read. These new reads can actually only read from the x := 1 write, because x := 1 was already observed by the preceding a := x read and overwrites the initialization write. Formally, if the b := x read were to read from the initialization write, the execution would be "inconsistent" as it would violate the "coherence" condition of RC11 (formally defined in §3). The algorithm detects this inconsistency before actually producing the inconsistent graph, and therefore does not waste time exploring it or any of its descendants.

The attentive reader may wonder why discarding these inconsistent executions is sound. If such executions *were* produced and further explored, could they eventually lead to some consistent execution? In fact, this cannot happen, because (in the absence of SC atomics) RC11-consistency is *prefix-determined* (Lemma 3.9 in §3.2.6). Roughly speaking, this means that if a read may read from some write after removing an ( $sb \cup rf$ )-suffix of the execution, then it may also read from that write when the suffix is included. (This property does not hold for SC, which forces us to treat SC atomics differently—see §2.5.3.)

#### 2.3 Ruling out Incoherent Executions

In the previous example, we saw a simple case where reading from a certain write was discarded because it would violate *coherence*. Specifically, after having observed a newer write, a thread cannot read from an older write (e.g., get  $a = 1 \land b = 0$  in co2rrw). More generally, coherence is a property provided by almost all memory models. It ensures that same-location writes are observed by all threads as happening in the same order.

In programs with concurrent writes to the same location, checking for coherence requires a bit more work than we have discussed so far. To illustrate this, consider the following program.

$$x := 1 \quad \left\| \begin{array}{c} x := 2 \end{array} \right\| \begin{array}{c} a := x; \\ b := x \end{array} \right\| \begin{array}{c} c := x; \\ d := x \end{array}$$

(CORR2)

Let us focus on the behavior where  $a = d = 1 \land b = c = 2$ , which is disallowed by RC11 (and any other memory model ensuring coherence), because the two threads observe the writes to *x* as happening in opposite orders.

To enforce coherence, RC11 executions are extended with a so-called "modification order" (mo). This is a union of total orders—each of which orders the writes to a particular memory location—that is used to impose certain consistency constraints requiring, e.g., that if a thread has observed a certain write, then it cannot later read from an mo-previous write. Thus, to generate all consistent executions, when adding a write to a graph, the exploration algorithm has to generate subexecutions for all the different places the write can be placed in mo. To avoid redundant explorations, special care is required while updating the set of revisitable reads in each subexecution. (We postpone these details to §4.3.)

In §5, we also consider a weaker model that does not fully ensure coherence for non-racy writes. This model, which we call WRC11 (for Weak RC11), does not record the modification order, which simplifies our exploration algorithm and lead to much fewer explored executions in various test cases. For example, in the **CORR2** program, recording **mo** yields 72 executions as opposed to 49 executions under WRC11 (of which 47 are coherent). We refer the reader to §5 for further details about WRC11.

#### 2.4 Handling Read-Modify-Write Instructions

We move on to read-modify-write (RMW) instructions, such as compare&exchange (a.k.a. compare&swap or CAS) and fetch&inc (FAI). These instructions combine a read and a write of the same location that are supposed to execute in one atomic step. We will refer to such reads and writes as *exclusive*. Some RMW instructions, such as fetch&inc, always produce two events, while others, such as compare&exchange, always generate the read event and only generate a write event if the read reads an appropriate value. Specifically, CAS(x, v, v') atomically reads x and if it has value v, replaces it with v' and returns true indicating that the CAS has succeeded (in updating x); otherwise it returns false indicating that the CAS has failed (to update x). The read of the CAS is considered exclusive only when the CAS succeeds. Atomicity of an RMW consisting of an exclusive read r and a write w means that there should not be any other event executed observably between r and w. In particular, two distinct exclusive reads cannot read from the same write event.

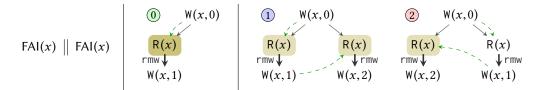

Handling RMWs adds a number of subtleties to the algorithm. To see them, let us start with the program shown in Fig. 4 consisting of two parallel atomic increments. After adding the events of the first thread, we reach the execution (1) shown in middle of the figure. We use thick edges to denote "RMW pairs" consisting of an exclusive read followed by an exclusive write to the same location. The goal is to generate all consistent executions of the program (i.e., executions (1) and (2) of Fig. 4 modulo the revisit sets).

Fig. 4. The FAIS program, an intermediate execution during its exploration, and its final executions.

Fig. 5. The LB+FAIS program together with the key step during its exploration.

The next event to add is the read of *x* from the second thread. This can read from two places—either from the write of the first thread or from the initialization write. In the former case, adding the write of the RMW yields execution (1) (ignoring the revisit set for now). When adding this write, the read of the first thread cannot be revisited because it precedes the write in  $(sb \cup rf)^+$ .

In the latter case, adding the write event of the RMW leads to an inconsistent execution: both RMWs are reading from the initialization write, thereby violating RMW atomicity. This violation, however, is only temporary: adding the write will lead to another execution, where the read of the first thread is revisited, eventually yielding the execution (2) (again, ignoring revisit sets).

The question remaining is what exactly to do with the revisit sets. For soundness, there are two properties that have to be satisfied. First, both executions 1 and 2 should have the later read (i.e., the one reading from the other RMW) as revisitable. This is needed to cover executions where the second RMW reads from a write after the first RMW (which might appear in some extension of the program with, say, a third thread performing x := 1). Second, at least one of the two executions should have the earlier read (i.e., the one reading from the initialization write) as revisitable. This is needed to cover executions where no RMW reads from the initial write, but rather from some write of a third thread. To satisfy these requirements, when adding a read, our algorithm chooses a write that is not read by an RMW as the one where the read is revisitable, and when revisiting a read, if this read is part of an RMW, it keeps it as revisitable. Returning to our example, the algorithm marks both reads of execution 1 and the read of the first thread of execution 2 as revisitable.

We note that the handling of RMWs, while sound, is not optimal. Consider, for example, an extension of FAIS with a third thread writing x := 42. Both executions (1) and (2) can be revisited. Moreover, in (1), revisiting the read of the first thread will cause the read of the second thread to be removed, and so, among other executions, the algorithm will visit the one where the FAI(x) of the first thread reads 0. This execution, however, is also generated by revisiting (2).

To illustrate in more detail how the revisit sets are calculated, we move on to the LB+FAIS example shown in Fig. 5, which is a variant of the "load buffering" litmus test with increments in the middle

of the two threads. Consider execution (3), which is generated by first adding all the events of the first thread and then the read of y from the initial write.

Adding the second FAI(z) generates executions (4) and (5). In (4), the second FAI(z) reads from the first one; its read is marked as revisitable and all other revisitable reads retain their status. In (5), the second FAI(z) reads from the initialization write. Its read becomes non-revisitable and so do all reads in its  $(sb \cup rf)$ -prefix (i.e., the read of y). Adding the write event of the increment causes the first increment to be revisited and read from the newly added write event. As discussed already, the read of the first thread's increment remains revisitable. Likewise, all reads in its  $(sb \cup rf)$ -prefix (i.e., the read of x) maintain their status. Retaining the revisitability of x is needed to cover the case where the read of x reads from the write of the second thread (to be added subsequently).

A more subtle difficulty arises in programs accessing the same location both using a CAS and using an always succeeding RMW such as FAI. Revisiting a read due to a failed CAS may change its status to that of a successful CAS; that is, the revisited read may turn into an exclusive read. This can conflict with another revisited exclusive read, leading to a temporary state, immediately after revisiting the two reads, where two pending exclusive reads both read from the same write. The conflict is resolved in the next step, when the write of the one exclusive read is added, which will force the other exclusive read to be revisited. An example demonstrating this subtlety is provided in §4.4.

#### 2.5 Handling Different Access Modes and Fences

In the examples so far, all memory accesses were treated following the semantics of RC11's *relaxed* atomic accesses. We will now show how the other access modes provided by RC11 are supported.

2.5.1 Release/acquire atomics. We start with release and acquire accesses, which are the simplest kind of accesses to handle. To handle those accesses, RC11 introduces the "happens before" order, hb, which is a generalization of the program order. It includes the program order, sb, a number of synchronization patterns, and any transitive combination thereof. The simplest synchronization pattern that induces hb ordering is when an acquire read operation reads from a release write as in the following "message passing" litmus test.

$$\begin{array}{c|c} x_{rlx} \coloneqq 1; \\ y_{rel} \coloneqq 1 \end{array} \begin{vmatrix} a \coloneqq y_{acq}; \\ b \coloneqq x_{rlx} \end{aligned} \tag{MP}$$

The outcome  $a = 1 \land b = 0$  is forbidden by RC11 because if a = 1, then the read of *y* synchronizes with the write of *y*, and thus the read of *x* is aware of the write of *x* (formally, the write of *x* happens before the read), which in turn means that the read of *x* cannot read from the overwritten initialization write. If we were to replace any of the two release/acquire accesses by relaxed accesses, the outcome  $a = 1 \land b = 0$  would become allowed, as relaxed accesses on their own do not induce any synchronization. Besides release and acquire accesses, RC11 also has release and acquire fences, whose use in combination with relaxed accesses results in similar synchronization patterns.

To handle release/acquire atomics, our algorithm maintains the happens before order. Whenever a read is added, as before, we consider all the writes that the read could read from without violating RC11's consistency constraints. Similarly, when a write is placed in mo, and when choosing possible reads to revisit after adding a write, we use the calculated hb relation to avoid violation of RC11's consistency constraints.

2.5.2 Non-atomic accesses. Next, we consider non-atomic accesses, which is the default accessing mode in C/C++ programs for variables that have not been declared as atomic. For such accesses, RC11 provides extremely weak semantics. Whenever a program contains a consistent execution with a data race involving non-atomic accesses, the program is deemed to have "undefined behavior"

Proceedings of the ACM on Programming Languages, Vol. 2, No. POPL, Article 17. Publication date: January 2018.

Fig. 6. The "store buffering" program with SC accesses, and its inconsistent execution.

(i.e., be erroneous). Therefore, to handle non-atomic accesses properly, we have to detect data races, i.e., concurrent accesses to the same location, at least one of which being a write, and at least one of which being non-atomic. To avoid redundant checks, it suffices to perform such a check whenever an access is added to the execution graph with respect to accesses already present. Thus, for every full execution of a program, each pair of accesses is checked only once, and moreover these checks are consolidated for all executions having that pair of accesses.

2.5.3 *SC atomics.* Finally, we consider SC accesses and fences, which can be used to impose strong global ordering between memory accesses, possibly leading to sequential consistency. The standard example demonstrating their use is the "store buffering" litmus test in Fig. 6. RC11 forbids the displayed execution with outcome a = b = 0, but allows it for the modified programs where one or more of the accesses are changed to have any non-SC mode. RC11 provides this semantics by defining a relation called psc ("partial SC order"), which it requires to be acyclic in every consistent execution. As psc is not necessarily included in  $(sb \cup rf)^+$ , the SC constraint of RC11 makes the model non-prefix-determined (see §2.2). Consequently, one *cannot* simply discard any executions with psc cycles during exploration. For example, suppose we extend the **SB** program with a third thread performing  $y_{sc} := 2$  (the access mode and value are immaterial) and we add the events from left to right. At some point during the exploration, we will reach the following execution shown to the right above, which is inconsistent according to RC11. If, however, we immediately discard it, we will fail to explore the execution resulting in  $a = 2 \land b = 0$ .

Thus, our algorithm does not check for psc-cycles during exploration. Instead, it checks for the absence of such cycles only before reporting an assertion violation or a forbidden data race. Naturally, this approach induces some redundant explorations, as certain psc-cycles may never be revisited and removed. As an optimization, psc-cycles due to non-revisitable events can be detected eagerly and discarded early.

#### 2.6 Handling Spin Loops and Assume Statements

Consider we want to verify a simple test-and-set lock implementation, and we construct a test case comprising of N parallel threads trying to acquire and immediately release a single lock as follows:

while

$$\neg CAS_{acq}(x,0,1)$$

do skip;

$x_{rel} := 1$  while  $\neg CAS_{acq}(x,0,1)$  do skip;

$x_{rel} := 1$

For N > 1, the CAS in the acquire loop can fail for an unbounded number of times as the lock may be held by another thread. Even with a moderate loop unrolling bound, explicitly recording these failed loop iterations in the executions can quickly lead to a huge number of executions to explore. Nevertheless, this exploration is completely redundant. Each time a CAS fails in the acquire loop, the thread reaches the exact same local state as if the failed CAS were never performed. Therefore, to get all the possible behaviors of this program, it suffices to consider the case where the CAS succeeds the first time it is performed. A standard way to achieve this is to perform a preprocessing

## 17:10 Michalis Kokologiannakis, Ori Lahav, Konstantinos Sagonas, and Viktor Vafeiadis

step and convert the program to the following one:

$$\begin{array}{l} a := \mathsf{CAS}_{\mathsf{acq}}(x,0,1); \text{ assume } (a); \\ x_{\mathsf{rel}} := 1 \end{array} \right\| \ \cdots \ \left\| \begin{array}{l} a := \mathsf{CAS}_{\mathsf{acq}}(x,0,1); \text{ assume } (a); \\ x_{\mathsf{rel}} := 1 \end{array} \right\|$$

replacing the CAS loop with its last iteration; namely, with the CAS followed by an **assume** statement reflecting the assumption that CAS succeeds. The question remaining is how to handle such **assume** statements. Clearly, their purpose is to rule out executions where the assumed condition is false. The subtlety is that one cannot always immediately rule out such executions when a false assumed condition is encountered. First, there may be an assertion violation (or a data race) in other (unexplored) threads. Additionally, there may be some revisitable nodes before the assume statement, whose revisiting may, for example, satisfy the assumed condition. For example, consider the exploration of the following program:

$$a := x_{rlx}$$

; assume  $(a \neq 0) \parallel x_{rlx} := 1 \parallel x_{rlx} := 2$

Here, adding the events of the first thread first would yield a revisitable read of x reading the value 0 from the initialization write, and a blocking **assume** statement. In such cases, we cannot stop the exploration, but rather have to continue adding events from other threads to see whether any of the events before the blocking **assume** will be revisited. Here, it would add the  $W^{rlx}(x, 1)$  event, which would generate a subexploration where the read of x is revisited. The exploration where the read is not revisited is then further explored so as to consider the case where it will be revisited by the write of the third thread. When, finally, all threads have either finished or are blocked (due to a failed assumption), we can discard the execution.

#### 3 THE RC11 MEMORY MODEL

In this section, we present our formal programming language semantics, following the RC11 memory model [Lahav et al. 2017]. This is done in three stages. First, in §3.1, we define the representation of programs. Then, in §3.2, we define execution graphs and RC11-consistency. Finally, in §3.3, we connect these two notions together and define when a program is erroneous.

# 3.1 Sequential Programs

For simplicity, we assume that, after preprocessing, programs are of the form  $||_{i \in Tid} P_i$ , where  $Tid = \{1, ..., N\}$  is a set of thread identifiers, and each  $P_i$  is a sequential loop-free deterministic program. We also assume finite sets Loc and Val of locations and values. The set of accesses and fences modes is given by Mod  $\triangleq$  {na,rlx,acq,rel,acqrel,sc}, and is partially ordered as follows:

$$na \sqsubset rlx \sqsubset acq \sqsubset acqrel \sqsubset sc$$

and  $rlx \sqsubset rel \sqsubset acqrel$ .

To refrain from setting a concrete syntax, we represent the sequential programs  $P_i$  as functions that return the *label* of the next action to execute given a (partial) program trace.

Definition 3.1. A label takes one of the following forms:

- read label:  $\mathbb{R}^{o}(x, V)$  where  $x \in \text{Loc}$ ,  $V \subseteq \text{Val}$ , and  $o \in \text{Mod}_{\mathbb{R}} \triangleq \{\text{na}, r \mid x, acq, sc\}$ . The set V stores all *exclusive values*: reading of which will make the read exclusive.

- write label:  $W^{o}(x, v)$  where  $x \in Loc, v \in Val$ , and  $o \in Mod_{W} \triangleq \{na, rlx, rel, sc\}$ .

- fence label:  $F^o$  where  $o \in Mod_F \triangleq \{acq, rel, acqrel, sc\}$ .

- error label: error.

- blocking label: block.

We denote the set of all labels by Lab. The functions typ, mod, loc, val, and exvals return (when applicable) a label's type (R/W/F/error/block), mode, location, written value, and exclusive values.

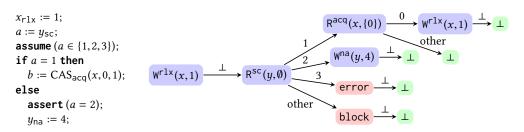

Fig. 7. Representation of a sequential program as a labeled automaton.

*Definition 3.2.* A *trace* is a finite sequence of Val  $\uplus$  { $\bot$ }. We denote by Trace the set of all traces. A sequential program is represented as a partial function  $P_i$  : Trace  $\rightarrow$  Lab.

To illustrate this representation, consider the program in Fig. 7 and its depiction as a labeled automaton. Each state is labeled with the label that is generated by that state, while the edges are labeled with the possible values that the state may return. In particular, states labeled with  $\perp$  are terminal states, states labeled with a read label have multiple next states—one for each value the read could return—and states labeled with other labels have exactly one next state. Reading this automaton as a function from traces to labels is straightforward. For example,  $P_i(\langle \perp, 1 \rangle) = \mathbb{R}^{acq}(x, \{0\})$ . Note that:

• The programming language semantics ensures that the next event of an exclusive read is its corresponding exclusive store, that is: whenever  $P_i(t) = \mathbb{R}^{o_{\mathbb{R}}}(x, V)$  and  $v_{\mathbb{R}} \in V$ , we have  $P_i(t \cdot \langle v_{\mathbb{R}} \rangle) = W^{o_{\mathbb{N}}}(x, v_{\mathbb{N}})$  for some  $o_{\mathbb{N}}, v_{\mathbb{N}}$  such that  $\langle o_{\mathbb{R}}, o_{\mathbb{N}} \rangle \in Mod_{\mathbb{R}M\mathbb{N}}$ , where:

$Mod_{RMW} \triangleq \{ \langle rlx, rlx \rangle, \langle acq, rlx \rangle, \langle rlx, rel \rangle, \langle acq, rel \rangle, \langle sc, sc \rangle \}$

These pairs stand for relaxed, acquire, release, acquire-release, and sequentially consistent RMW operations, respectively.

• Error and blocking labels block the execution: if  $P_i(t) \in \{\text{error}, \text{block}\}, \text{ then } P_i(t \cdot \langle \perp \rangle) = \perp$ .

#### 3.2 Execution Graphs

Next, we formally introduce execution graphs and the RC11-consistency constraints.

Before we start, we introduce some notation. Given a binary relation R, dom(R) and codom(R) denote its domain and codomain. Further, we write  $R^{?}$ ,  $R^{+}$ , and  $R^{*}$  respectively to denote its reflexive, transitive, and reflexive-transitive closures. The inverse relation is denoted by  $R^{-1}$ . We denote by  $R_1$ ;  $R_2$  the left composition of two relations  $R_1$ ,  $R_2$ , and assume that ; binds tighter than  $\cup$  and  $\setminus$ . We denote by [A] the identity relation on a set A. In particular, [A]; R;  $[B] = R \cap (A \times B)$ . We omit the set parentheses when writing expressions like  $[a_1, \ldots, a_n]$  (which stands for  $\{\langle a_1, a_1 \rangle, \ldots, \langle a_n, a_n \rangle\}$ ). Finally, given an element a, succ<sub>R</sub>(a) denotes the unique element b such that  $\langle a, c \rangle \in R \Leftrightarrow \langle b, c \rangle \in R^{?}$  for every c (undefined if such an element does not exist or is not unique).

Definition 3.3. An event is a tuple  $\langle i, n, l \rangle \in (\text{Tid} \cup \{0\}) \times \mathbb{N} \times \text{Lab}$ , where *i* is a thread identifier (0 for initialization events), *n* is a serial number inside each thread, and *l* is a label. The functions tid and lab return the thread identifier and the label of an event. In addition, the functions typ, mod, loc, val, and exvals are extended to events in the obvious way. We denote the set of all events by E, and use R,W,F,error,block to denote the set of events of the respective type. We use subscripts and superscripts to denote the accessed location, the thread identifier, and the mode (e.g.,  $\mathsf{E}^i = \{a \in \mathsf{E} \mid \mathsf{tid}(a) = i\}$  and  $\mathsf{W}_x^{\exists rel} = \{w \in \mathsf{W} \mid \mathsf{loc}(w) = x \land \mathsf{mod}(w) \sqsupseteq \mathsf{rel}\}$ ).

Definition 3.4. The set  $E_0$  of initialization events is given by  $E_0 \triangleq \{(0,0, W^{na}(x,0)) \mid x \in Loc\}$ .

Definition 3.5. The sequenced-before relation, denoted sb, is given by:

$\mathsf{sb} \triangleq \mathsf{E}_0 \times (\mathsf{E} \setminus \mathsf{E}_0) \cup \{ \langle \langle i_1, n_1, l_1 \rangle, \langle i_2, n_2, l_2 \rangle \rangle \in (\mathsf{E} \setminus \mathsf{E}_0) \times (\mathsf{E} \setminus \mathsf{E}_0) \mid i_1 = i_2 \land n_1 < n_2 \}$

*Definition 3.6.* An *execution G* is a tuple  $\langle E, rf, mo \rangle$  where:

- (1) *E* is a finite set of events containing the set  $E_0$  of initialization events.

- (2) *rf*, called *reads-from*, is a binary relation on *E* satisfying:

- $w \in W, r \in \mathbb{R}$  and loc(w) = loc(r) for every  $\langle w, r \rangle \in rf$ .

- $w_1 = w_2$  whenever  $\langle w_1, r \rangle, \langle w_2, r \rangle \in rf$  (that is  $rf^{-1}$  is a partial function).

- (3) *mo*, called *modification order*, is a disjoint union of relations  $\{mo_x\}_{x \in Loc}$ , such that each  $mo_x$  is a strict partial order on  $E \cap W_x$ .

We denote the components of an execution  $G = \langle E, rf, mo \rangle$  by G.E, G.rf and G.mo. In addition, G induces the following sets, functions and relations:

- $G.val_r : E \rightarrow Val$  returns the value read by event r, that is:  $G.val_r(r) = val(w)$  where w is the (unique) write such that  $\langle w, r \rangle \in rf$ . If r is not a read event or such a write does not exist, then  $G.val_r(r) = \bot$ .

- G.sb is given by  $G.sb \triangleq [G.E]; sb; [G.E].$

- A read event  $r \in E$  is called *exclusive* in G if  $G.val_r(r) \in exvals(r)$ . We write  $G.R^{ex}$  to denote the set of exclusive reads in G.

- *G*.rmw, called *read-modify-write pairs*, is the relation given by *G*.rmw =  $[G.R^{ex}]$ ; *G*.sb|<sub>imm</sub>, where sb|<sub>imm</sub> = sb \ (sb; sb). (Note that for executions resulting from programs we have  $w \in W$ , loc(r) = loc(w) and  $(mod(r), mod(w)) \in Mod_{RMW}$  for every  $(r, w) \in G.rmw$ .)

The main part of the memory model is filtering the consistent executions among all executions of the program by imposing certain constraints.

3.2.1 *Completeness.* The first constraint is very simple: every read should read a value. Accordingly, we call an execution G is called *complete* if  $G.E \cap R \subseteq codom(G.rf)$ .

3.2.2 *Coherence.* Coherence (a.k.a. SC-per-location) requires that, for every particular location, all threads agree on the order of accesses to that location. Moreover, this order should be consistent with the *happens-before* order (hb), which intuitively records when an event is globally perceived as occurring before another one. To define hb, several derived relations are needed:

$$G.\mathsf{rseq} \triangleq \bigcup_{x \in \mathsf{Loc}} [\mathsf{W}_x]; G.\mathsf{sb}^?; [\mathsf{W}_x^{\exists r \mathsf{l} x}]; (G.\mathsf{rf}; G.\mathsf{rmw})^* \qquad (release \ sequence)$$

$$G.\mathsf{sw} \triangleq [\mathsf{E}^{\exists rel}]; ([\mathsf{F}]; G.\mathsf{sb})^?; G.\mathsf{rseq}; G.\mathsf{rf}; [\mathsf{R}^{\exists r \mathsf{l} x}]; (G.\mathsf{sb}; [\mathsf{F}])^?; [\mathsf{E}^{\exists \mathsf{acq}}] \qquad (synchronizes \ with)$$

$$G.\mathsf{hb} \triangleq (G.\mathsf{sb} \cup G.\mathsf{sw})^+ \qquad (happens-before)$$

Happens-before is defined in terms of two more basic definitions. First, the *release sequence* (rseq) of a write contains the write itself and all later writes to the same location in the same thread, as well as all RMWs that recursively read from such writes. Next, a release event *a synchronizes with* (sw) an acquire event *b*, whenever *b* (or, in case *b* is a fence, some sb-prior read) reads from the release sequence of *a* (or, in case *a* is a fence, of some sb-later write). Finally, we say that an event *a happens-before* another event *b* if there is a path from *a* to *b* consisting of sb and sw edges.

To order accesses to a given location, the model requires that for every location x, G.mo totally orders the writes to x, and defines an extension of mo, which is a partial order on all accesses to x:

$G.eco \triangleq (G.mo \cup G.rf \cup G.rf^{-1}; G.mo)^+$  (extended coherence order)

Here, writes are ordered using mo, while reads are placed after the writes they read from, but before writes that are mo-later than the writes they read from. Then, the coherence condition simply requires that G.eco; G.hb is irreflexive.

Proceedings of the ACM on Programming Languages, Vol. 2, No. POPL, Article 17. Publication date: January 2018.

Note that, assuming the *G*.mo totally orders same-location writes, an equivalent definition of the extended coherence order is given by  $G.eco = G.mo; G.rf^? \cup G.rf \cup G.rf^{-1}; G.mo; G.rf^?$ .

3.2.3 Atomicity. The atomicity constraint requires that for every pair  $\langle r, w \rangle \in G.$ rmw, there is no event in modification order between the write from which r reads-from and w. Accordingly, it requires that G.rf; G.rmw; G.mo<sup>-1</sup>; G.mo<sup>-1</sup> is irreflexive.

In particular, this condition (together with totality of mo) disallows two RMWs to read from the same write (i.e., G.rf; G.rmw is partial function). Note, however, if some exclusive read is sb-maximal it may read from a write that is read by another exclusive read (as, e.g., happens during the exploration of FAIs in §2.4). We refer to sb-maximal exclusive reads as *pending RMWs*, because their corresponding write event has not been added to the execution yet, and denote this set by  $G.R_{pending}^{ex}$  (formally,  $G.R_{pending}^{ex} \triangleq G.R^{ex} \setminus dom(G.rmw)$ ).

3.2.4 Global SC constraint. SC accesses and fences are subject to a global constraint, which, roughly speaking, requires threads to agree on their order. In fact, due to the interaction with other access modes, this is notably the most involved part of RC11, which addresses flaws of the original C/C++ memory model. The repaired SC condition requires the acyclicity of a relation called *partial SC order*, denoted psc, which is, in turn, defined using additional helper notations (we refer the reader to Lahav et al. [2017] for detailed explanations):

$$\begin{aligned} G.\text{sb}|_{\neq \text{loc}} &\triangleq \{\langle a,b \rangle \in G.\text{sb} \mid \text{loc}(a) \neq \text{loc}(b)\} & G.\text{hb}|_{\text{loc}} \triangleq \{\langle a,b \rangle \in G.\text{hb} \mid \text{loc}(a) = \text{loc}(b)\} \\ G.\text{scb} &\triangleq G.\text{sb} \cup G.\text{sb}|_{\neq \text{loc}}; G.\text{hb}; G.\text{sb}|_{\neq \text{loc}} \cup G.\text{hb}|_{\text{loc}} \cup G.\text{mo} \cup G.\text{rf}^{-1}; G.\text{mo} \quad (SC\text{-before}) \\ G.\text{psc} &\triangleq ([\mathsf{E}^{\text{sc}}] \cup [\mathsf{F}^{\text{sc}}]; G.\text{hb}^{2}); G.\text{scb}; ([\mathsf{E}^{\text{sc}}] \cup G.\text{hb}^{2}; [\mathsf{F}^{\text{sc}}]) \cup \\ & [\mathsf{F}^{\text{sc}}]; (G.\text{hb} \cup G.\text{hb}; G.\text{eco}; G.\text{hb}); [\mathsf{F}^{\text{sc}}] \quad (partial SC order) \end{aligned}$$

3.2.5 No sb $\cup$ rf cycles. Finally, in order to rule out "out-of-thin-air" behaviors, where reads can return arbitrary values due to cyclic dependencies, RC11 adopts a conservative fix over the original C/C++11 model suggested by Vafeiadis and Narayan [2013] and Boehm and Demsky [2014]. It requires that the relation G.sbrf  $\triangleq$  (G.sb $\cup$ G.rf)<sup>+</sup> is irreflexive.

3.2.6 RC11 consistency. Summarizing the constraints above, we define RC11-consistency.

*Definition 3.7.* An execution *G* is RC11-*consistent* if the following hold:

| • <i>G</i> is complete.                                                                                | (COMPLETENESS)  |

|--------------------------------------------------------------------------------------------------------|-----------------|

| • For every location $x$ , $G$ .mo totally orders $G$ . $E \cap W_x$ .                                 | (valid mo)      |

| • <i>G</i> .eco; <i>G</i> .hb is irreflexive.                                                          | (COHERENCE)     |

| • <i>G</i> .rf; <i>G</i> .rmw; <i>G</i> .mo <sup>-1</sup> ; <i>G</i> .mo <sup>-1</sup> is irreflexive. | (ATOMICITY)     |

| • G.psc is acyclic.                                                                                    | (SC-ACYCLICITY) |

| • G.sbrf is irreflexive.                                                                               | (SBRF)          |

We will refer to executions that satisfy all conditions except (possibly) for <u>sc-acyclicity</u> as RC11preconsistent executions.

Next, we can formally state the "prefix-closedness" and "prefix-determinedness" properties mentioned earlier. For a set *E* such that  $dom(sbrf; [E]) \subseteq E$ , Restrict(*G*, *E*) denotes the execution *G*' given by *G*'.E = *E*, *G*'.rf = [*E*]; *G*.rf; [*E*], and *G*'.mo = [*E*]; *G*.mo; [*E*].

LEMMA 3.8 (PREFIX-CLOSED). If G is RC11-(pre)consistent, then so is Restrict(G, E) for every  $E \subseteq G$ .E such that dom(sbrf;  $[E]) \subseteq E$ .

**PROOF.** Let G' = Restrict(G, E). It is easy to see that for every relation *R* mentioned above, we have G'.R = [E]; G.R; [E]. The claim follows observing that all conditions in Def. 3.7, except for

**COMPLETENESS**, are monotone: if they hold for larger relations, they also hold for smaller ones. Finally, completeness of *G*' follows from the completeness of *G* and the fact that  $dom(rf; [E]) \subseteq E$ .  $\Box$

LEMMA 3.9 (PREFIX-DETERMINED). Let r be an sb-maximal read event in an execution G. If both Restrict(G, G.  $\{r\}$ ) and Restrict(G, dom(G. sbrf<sup>?</sup>; [r])) are RC11-preconsistent, then so is G.

PROOF. Easily follows from the definitions: any violation of one of the consistency conditions (except for sc-acyclicity) is a violation of the same condition either in Restrict( $G, G. \in \{r\}$ ) (if the violation does not involve r) or in Restrict( $G, dom(G.sbrf^?; [r])$ ) (if the violation involves r). For example, consider a violation of COHERENCE, i.e., a pair  $\langle a, b \rangle \in G.$ hb such that  $\langle b, a \rangle \in G.$ eco. If  $\langle b, r \rangle \in G.sbrf^2$ , then, since  $G.hb \subseteq G.sbrf$ , we have also  $\langle a, r \rangle \in G.sbrf$ . Hence,  $a, b \in dom(G.sbrf^?; [r])$ , and it follows that  $\langle a, b \rangle \in G'.$ hb and  $\langle b, a \rangle \in G'.$ eco, where  $G' = Restrict(G, dom(G.sbrf^?; [r]))$ . Thus, COHERENCE is violated also in Restrict( $G, dom(G.sbrf^?; [r])$ ). Alternatively, if  $\langle b, r \rangle \notin G.sbrf^2$ , we have that  $b \neq r$ , as well as  $a \neq r$  (since r is hb-maximal in G), and so COHERENCE is violated also in Restrict( $G, G.E \setminus \{r\}$ ).

Note that SC is not prefix-determined (and thus, RC11-consistency is not prefix-determined due to sc-ACYCLICITY). Indeed, consider the execution of the "store buffering" program in Fig. 6, and let r be any of the two reads in this execution. The executions Restrict( $G, G.E \setminus \{r\}$ ) and Restrict( $G, dom(G.sbrf^2; [r])$ ) are both SC-consistent, but G is not.

#### 3.3 Semantics of Concurrent Programs

To complete the description of the concurrency semantics, we explain how traces of sequential programs and RC11-consistent executions interact.

First, from a given complete execution graph, one can easily extract a trace for each thread. Formally, trace(G, i) =  $\langle G.val_r(a_1), ..., G.val_r(a_n) \rangle$  where  $a_1, ..., a_n$  is the enumeration of  $G.E \cap E_i$  following sb. Then, we say that G is an *execution of* a program  $P = ||_{i \in Tid} P_i$  if for every thread  $i \in Tid$  and a proper prefix t of length n of trace(G, i), we have  $P_i(t) = lab(a)$  where a is the n + 1 event (following sb) in  $G.E \cap E_i$ . In turn, G is called *full* if  $P_i(trace(G, i)) = \bot$  for every thread  $i \in Tid$ .

Now, we can define when a program is *erroneous*. There are two kinds of errors. The first is an assertion violation indicated by an error event in some consistent execution of the program. The second is a forbidden data race (a race that involves a non-atomic access) as defined next.

Definition 3.10. Two events  $a, b \in E$  are called *conflicting* if  $W \in \{typ(a), typ(b)\}, a \neq b$ , and loc(a) = loc(b). A pair  $\langle a, b \rangle$  is called a *race* in an execution *G* (denoted  $\langle a, b \rangle \in G$ .race) if *a* and *b* are conflicting,  $a, b \in G$ .E,  $na \in \{mod(a), mod(b)\}$ , and  $\langle a, b \rangle \notin G$ .hb  $\cup G$ .hb<sup>-1</sup>.

*Remark 1.* One subtle point to note is that non-atomic reads may still be involved in a race even if they can read from only one write. For example, the only consistent execution of the program

$$x_{rlx} := 1 || a := x_{rlx}$$

; if a then  $b := x_{na}$

containing a non-atomic read is one where the relaxed read of *x* reads the value 1. In this case, however, the non-atomic read cannot read 0, because that violates **COHERENCE**. Nevertheless, it does race with the  $x_{r1x} := 1$  because there is no hb between the two events. (Recall that reads-from between relaxed accesses does not contribute to happens-before).

Definition 3.11. A program *P* is erroneous if there exists an RC11-consistent execution *G* of *P* such that either  $G.E \cap \text{error} \neq \emptyset$  or  $G.\text{race} \neq \emptyset$ .

| Alg | <b>gorithm 1</b> Main exploration         | ion algorithm.                                     |                                                  |

|-----|-------------------------------------------|----------------------------------------------------|--------------------------------------------------|

| 1:  | <pre>procedure Visit(G,T)</pre>           |                                                    |                                                  |

| 2:  | $a \leftarrow \operatorname{next}_P(G,T)$ |                                                    |                                                  |

| 3:  | if $a \neq \bot$ then                     |                                                    |                                                  |

| 4:  | $G \leftarrow Add(G, a)$                  |                                                    |                                                  |

| 5:  | <b>switch</b> typ(a) <b>d</b>             | D                                                  |                                                  |

| 6:  | case R                                    | VISITREAD $(G, T, a)$                              | Handling a read event                            |

| 7:  | case W                                    | VISITWRITE $(G, T, a)$                             | ▹ Handling a write event                         |

| 8:  | otherwise                                 | VISIT(G,T)                                         | ▶ Handling a fence, a blocked, or an error event |

| 9:  | else if ( $G.E \cap error$                | $\neq \emptyset \lor G.race \neq \emptyset) \land$ | (G.psc is acyclic) <b>then</b>                   |

| 10: | <pre>exit(erroneous</pre>                 | program)                                           |                                                  |

#### 4 **OUR MODEL CHECKING ALGORITHM**

In this section, we present our algorithm for model checking concurrent programs under RC11. Consider a program  $P = \prod_{i \in Tid} P_i$ , where each  $P_i$  is a sequential loop-free deterministic program. As outlined above, the algorithm maintains a collection of program executions annotated with a set of "revisitable" reads. We refer to such pairs as configurations:

Definition 4.1. A configuration (of program P) is a pair (G, T), where G is an RC11-preconsistent execution of *P* and  $T \subseteq G.E \cap R$  is a set of *revisitable read events* such that the following hold:

- (1)  $codom([T]; G.sbrf; [R]) \subseteq T.$

- (2) [G.R<sup>ex</sup><sub>pending</sub>]; G.rf<sup>-1</sup>; G.rf; [G.R<sup>ex</sup> \ G.R<sup>ex</sup><sub>pending</sub>] ⊆ (E \ T) × T.

(3) G.R<sup>ex</sup><sub>pending</sub> is either empty, a singleton, or consists of two events reading from the same write, one revisitable and one not-namely, two events  $(r,t) \in [E \setminus T]; G.rf^{-1}; G.rf; [T]$ .

Our exploration algorithm maintains the conditions in Def. 4.1 by construction. The first condition observes that the revisit set is sbrf-closed; i.e., if an event is revisitable, then so are all its sbrflater read events. Condition 2 requires that if the graph contains a pending exclusive read r and non-pending exclusive read t, reading from the same write, then t must be revisitable and rshould not. The requirement that t is revisitable is to avoid latent atomicity violations (otherwise, atomicity would be violated by adding r's corresponding exclusive write to the execution). Finally, condition 3 ensures that pending exclusive reads are completed as soon as possible by adding their corresponding exclusive writes. (Once an execution has a pending exclusive read, the next event to add is its corresponding write.) During the revisiting of read events due to CAS instructions, however, it may also happen that two reads reading from the same write may become simultaneously pending; this will be explained in §4.4.

To decide on the order in which events are added to G, the exploration algorithm assumes the existence of a partial function, next<sub>P</sub> : Configuration  $\rightarrow E$ , that given a configuration  $\langle G, T \rangle$  of P generates a new event to be added to G. The function  $next_P$  could be implemented by choosing a thread  $i \in \text{Tid}$  such that  $P_i(\text{trace}(G, i)) \neq \bot$ , and taking  $\text{next}_P(G, T)$  to be  $\langle i, |G. \mathsf{E} \cap \mathsf{E}_i| + 1, P_i(\text{trace}(G, i)) \rangle$ . For correctness, the choice of *i* should satisfy the following:

- (1) If  $G.R_{\text{pending}}^{\text{ex}} = \{r\}$  then i = tid(r).

- (2) Otherwise, if  $G.R_{\text{pending}}^{\text{ex}} = \{r, t\}$  where  $r \notin T$  and  $t \in T$ , then i = tid(r).

- (3) Otherwise, *i* can be chosen arbitrarily among all threads that are not blocked or finished. (In our implementation, we just select the one with the smallest identifier.)

The function next<sub>P</sub> returns  $\perp$  whenever either all threads have finished or are blocked.

Algorithm 2 Visiting a read r, which involves calculating where r could read from.

1: **procedure** VISITREAD(G, T, r) $W \leftarrow G. \mathsf{E} \cap \mathsf{W}_{\mathsf{loc}(r)}$ ▷ Consider all the writes in *G* from where to read 2:  $W \leftarrow W \setminus dom(G.mo; G.rf^?; G.hb; [r])$ ▶ Remove ones that would violate COHERENCE 3:  $A_1 \leftarrow \{w \in \mathbb{W} \mid \mathsf{val}(w) \in \mathsf{exvals}(r)\}$ 4:  $A_2 \leftarrow dom(G.rf; ([G.R^{ex} \setminus T] \cup [G.R^{ex} \cap T]; G.sbrf; [r]))$ 5:  $W \leftarrow W \setminus (A_1 \cap A_2)$ ▶ Remove ones that would violate **ATOMICITY** 6: **choose some**  $w_0 \in W \cap dom(G.sbrf; [r])$ 7: while val( $w_0$ )  $\in$  exvals(r)  $\land$  codom([ $w_0$ ]; G.rf; G.rmw)  $\neq \emptyset$  do 8:  $\{w_0\} \leftarrow codom([w_0]; G.rf; G.rmw)$ 9: VISIT(SetRF( $G, w_0, \{r\}$ ),  $T \cup \{r\}$ ) 10: for  $w \in W \setminus \{w_0\}$  do VISIT(SetRF( $G, w, \{r\}$ ),  $T \setminus dom(G.sbrf; [r, w]$ )) 11:

## 4.1 The Main Routine

A pseudocode implementation of the exploration algorithm is given in Algorithm 1. The procedure VISIT(G, T) explores all the configurations of the program P that are reachable from the configuration  $\langle G, T \rangle$ . Initially, it is called with the initial graph  $G_0$  containing only the initialization writes  $\mathsf{E}_0$  and the empty revisit set  $T_0 = \emptyset$ .

VISIT first calls  $next_P(G,T)$  to return the next new event to be added. If a concrete event is returned, it is added to the execution graph by putting it at the end of the appropriate thread of the graph. This is done using the following construction:

Definition 4.2 (Addition). For an event  $a = \langle i, |G.E \cap E_i| + 1, l \rangle$ , Add(*G*, *a*) is the execution *G*' given by  $G'.E = G.E \uplus \{a\}, G'.rf = G.rf$ , and G'.mo = G.mo.

Depending on whether the new event, *a*, is a read, a write, or some other event, VISIT then calls VISITREAD, VISITWRITE or VISIT recursively. If no event is returned, it means that we have reached a full execution. If the execution contains an error or a race and also satisfies the sc-acyclicity constraint, the exploration terminates and reports an error.

*Remark 2.* Our implementation of Algorithm 1 improves it in a few simple ways. When an error or a racy event is added to an execution, if the execution satisfies **SC-ACYCLICITY**, the error is reported immediately. Similarly, when a blocked event is added and its sbrf-prefix contains no revisitable reads and at least one non-revisitable read, further exploration is aborted. Indeed, in this case, our construction ensures that there is another execution with a revisitable read sbrf-before the blocked event, whose exploration is not aborted.

#### 4.2 The VISITREAD Procedure (Algorithm 2)

VISITREAD calculates the set of writes W that the read r could possibly read from. These are the set of all writes to the same location as r that belong to the execution graph G, where reading from them violates neither COHERENCE nor ATOMICITY. Coherence is violated by reading from a write that reaches r via mo;  $rf^2$ ; hb because then eco would contradict hb. Atomicity is violated by reading from a write in  $A_1 \cap A_2$ ; reading from these writes would make the read r become RMW event (cf. the set  $A_1$ ), and moreover, these writes are already read by a non-revisitable RMW or by a revisitable RMW that is G.sbrf-before r (cf. the set  $A_2$ ).

Then, lines 7–9 concern choosing an appropriate default write  $w_0$  from the set *W*. Reading from that write makes the read *r* revisitable (line 10), whereas reading from any other write *w* not

| •           | · · · ·                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1: <b>p</b> | rocedure VISITWRITE(G,T,w)                                                                                                        |

| 2:          | if $\exists w_p, \langle w_p, w \rangle \in G.rf; G.rmw$ then                                                                     |

| 3:          | $RevisitReads(InsertMO(G, w_p, w), T, w)$                                                                                         |

| 4:          | else                                                                                                                              |

| 5:          | $w_0 \leftarrow \max_{G.mo} W_{loc(w)}$                                                                                           |

| 6:          | RevisitReads(Insert $MO(G, w_0, w), T, w$ )                                                                                       |

| 7:          | <b>for</b> $w_p \in G.E \cap W_{loc(w)} \setminus \{w_0\} \setminus dom(G.rf; [G.R^{ex}] \cup G.mo; G.rf^?; G.hb; [w])$ <b>do</b> |

| 8:          | REVISITREADS(InsertMO( $G, w_p, w$ ), $T \setminus dom(G.sbrf; [w, succ_{G.mo}(w_p)]), w$ )                                       |

|             |                                                                                                                                   |

Algorithm 3 Visiting a write w, which involves adding it in mo and revisiting any relevant reads.

only makes the read r non-revisitable but also makes any reads in the sbrf-prefix of w or of r non-revisitable (line 11). Adding the new reads-from edge is done via the following construction:

Definition 4.3 (rf-setting). For an event  $w \in G.E \cap W$  and a set  $R \subseteq G.E \cap R_{loc(w)}$ , SetRF(G, w, R) is the execution G' given by  $G'.E = G.E, G'.rf = G.rf \setminus (E \times R) \cup (\{w\} \times R)$ , and G'.mo = G.mo.

We note that the actual choice of  $w_0 \in W$  is not important for soundness, but it affects termination and our optimality result. We generally prefer to read from some sbrf-prior event, as this is needed for optimality. If the chosen  $w_0$  is already read by an exclusive read and reading from  $w_0$  would also make r exclusive, we select the next event down the rf; rmw chain. (The latter is needed to ensure termination, e.g., for the program consisting of three parallel FAI(x) instructions.)

#### 4.3 The VISITWRITE Procedure (Algorithm 3)

We proceed to the case when a write *w* is added to an execution graph *G*. VISITWRITE determines the possible places of the write in the modification order for the location it writes to, and then for each such place, it calls the REVISITREADS procedure to determine all the ways in which existing reads could be revisited to read from the newly added write *w*. If the write is exclusive (i.e., a part of an RMW instruction), then its placement in mo is unique: it must immediately follow the write,  $w_p$ , from which the read event of the RMW reads (cf. lines 2–3).

Otherwise, w can be placed after the maximal write in mo as well as immediately after any other write  $w_p$  that is not read by an exclusive read and that is not mo-overwritten by another write  $rf^?$ ; hb before w. To see why the latter condition is necessary consider  $w_p$  had some mo-successor  $w_n$  that is  $rf^?$ ; hb before w. Placing w immediately after  $w_p$  would place it before  $w_n$  and would thus result in a mo;  $rf^?$ ; hb cycle, thereby violating COHERENCE. In case the write is placed between some  $\langle w_p, w_n \rangle$  pair in G.mo where  $w_n = \operatorname{succ}_{G.mo}(w_p)$ , we additionally remove any events in the sbrf-prefixes of w and of  $w_n$  from the revisit set.

The reason why the sbrf-prefixes of w are removed from the revisit set is analogous to that for removing the sbrf-prefixes of the read r in the VISITREAD procedure in all but one subexplorations. Namely, revisiting some read sbrf-before w will remove w and so its placement in the mo-order in those revisited executions is irrelevant. It, therefore, suffices to have the sbrf-prefix of w retain its revisitability status in one subexploration—here, we take the one where w becomes mo-maximal.

The reason why the sbrf-prefixes of  $w_n$  are also removed from the revisit set is similar. First note that the execution  $G_p$  where w is placed immediately after  $w_p$  and the execution  $G_n$  where wis placed immediately after  $w_n$  differ only in the relative order of w and  $w_n$  in mo. (In particular,  $G_p.mo \setminus \{\langle w, w_n \rangle\} = G_n.mo \setminus \{\langle w_n, w \rangle\}$ .) Now consider some read before  $w_n$  is revisited, and so  $w_n$ is removed from the execution. Then, in those revisited executions, the relative placement of w and  $w_n$  in mo is irrelevant; so it does not matter whether these executions get generated by revisiting

| Algorithm 4 Procedure for re- | visiting reads (for the case t | hat w is not exclusive). |

|-------------------------------|--------------------------------|--------------------------|

|-------------------------------|--------------------------------|--------------------------|

| 1: <b>p</b> | rocedure RevisitReads(G,T,w)                                                        |                                                         |

|-------------|-------------------------------------------------------------------------------------|---------------------------------------------------------|

| 2:          | $R \leftarrow T \cap R_{loc(w)}$                                                    | ▶ Revisitable reads of the same location                |

| 3:          | $R \leftarrow R \setminus dom(G.sbrf;[w])$                                          | Discard ones violating SBRF                             |

| 4:          | $R \leftarrow R \setminus codom([w]; G.mo; G.rf^?; G.hb^?; G.sb)$                   | Discard ones violating COHERENCE                        |

| 5:          | <b>for</b> $K \subseteq R$ such that $[K]; G.$ sbrf; $[K] = \emptyset \land  \{r\}$ | $r \in K \mid val(w) \in exvals(r)\} \leq 1$ do         |

| 6:          | $G' \leftarrow Remove(G, \mathit{codom}([K]; G.sbrf))$                              | Remove sbrf-successors of K                             |

| 7:          | $G' \leftarrow SetRF(G', w, K)$                                                     | ▶ Make the <i>K</i> reads read from <i>w</i>            |

| 8:          | $T' \leftarrow (T \cap G'.E) \setminus dom(G'.sbrf^?;[K])$                          | <ul> <li>Adjust the set of revisitable reads</li> </ul> |

| 9:          | VISIT(G',T')                                                                        |                                                         |

$G_p$  or  $G_n$ . Therefore, to avoid duplication, we pick  $G_n$  as the preferred execution, and so remove the sbrf-prefixes of  $w_n$  from  $G_p$ .

Finally, the adjustment of G.mo is done using the following construction.

Definition 4.4 (mo-placement). For an event  $w \in G.E \cap W \setminus (dom(G.mo) \cup codom(G.mo))$  and event  $w_p \in G.E \cap W_{loc(w)}$ , InsertMO( $G, w_p, w$ ) is the execution G' given by G'.E = G.E, G'.rf = G.rf, and  $G'.mo = G.mo \cup (dom(G.mo^?; [w_p]) \times \{w\}) \cup (\{w\} \times codom([w_p]; G.mo))$ .

Finally, for all the valid mo-placements of the write *w*, VISITWRITE calls the REVISITREADS procedure to consider which reads may and/or should be revisited.

#### 4.4 The REVISITREADS Procedure (Algorithms 4 and 5)

The REVISITREADS procedure is the most involved part of our algorithm. We present its pseudocode in Algorithm 4, first for the easier case when the freshly added write is not exclusive.

First, REVISITREADS calculates the set of reads that may be revisited to read from the freshly added write w. We start with all the revisitable reads to the same location as w (line 2) and remove ones which if they were to read from w would result in a sbrf-cycle thereby violating SBRF (line 3) as well as those which if they were to read from w would result in a coherence violation (line 4).

Then, we consider revisiting every subset K of the relevant revisitable reads. To ensure that the revisits do not introduce any latent **ATOMICITY** violations, at line 5, we require that at most one read in K will become part of a RMW by the change. Note that when a set of reads K is revisited, the values returned by those reads may change; so all the sbrf-successors of K have to be removed from the execution. Accordingly, line 6 creates a copy, G', of the execution containing all the events that are not sbrf-after K, using the following construction:

Definition 4.5 (Removal). For a set  $E' \subseteq G.E$  such that  $codom([E']; G.sbrf) \subseteq E'$ , we denote by Remove(G, E') the execution G' given by  $G'.E = G.E \setminus E', G'.rf = [G'.E]; G.rf; [G'.E]$ , and G'.mo = [G'.E]; G.mo; [G'.E].

Then, line 7 changes the rf-edges of K to read from the new write w (see Def. 4.3). Line 8 adjusts the revisit set by removing all reads in the sbrf-prefix of K, and then the subexecution is further explored.

The case where w is exclusive (i.e.,  $w \in codom(G.rmw)$ ) requires more careful attention. Its pseudocode is given in Algorithm 5 (which, in fact, generalizes Algorithm 4). In addition to the description above, this procedure checks whether there exist any writes  $K_{must}$  that *must* be revisited, because otherwise **ATOMICITY** would be violated (line 5). Note that if w is not exclusive, then  $K_{must} = \emptyset$ . If, however, w together with some read r form an RMW, then  $K_{must}$  contains the (at most one) exclusive read other than r that reads from the same write as r does, if such a read exists.

Algorithm 5 Procedure for revisiting reads after a write is added (general case).

| 1: p | procedure RevisitReads(G,T,w)                                                     |                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:   | $R \leftarrow T \cap R_{loc(w)}$                                                  | ▶ Revisitable reads of the same location                                                                                                                                         |

| 3:   | $R \leftarrow R \setminus dom(G.sbrf; [w])$                                       | Discard ones violating SBRF                                                                                                                                                      |

| 4:   | $R \leftarrow R \setminus codom([w]; G.mo; G.rf^?; G.hb^?; G.sb)$                 | Discard ones violating COHERENCE                                                                                                                                                 |

| 5:   | $K_{\text{must}} \leftarrow dom([G.R^{\text{ex}}]; G.rf^{-1}; G.rf; G.rmw; [w])$  | $V ] \setminus G.rmw$ $\triangleright K_{must}$ must be revisited                                                                                                                |

| 6:   | $R \leftarrow R \setminus codom([K_{must}]; G.sbrf?) > T$                         | he remaining ones, whose revisit is optional                                                                                                                                     |

| 7:   | <b>for</b> $K_1 \subseteq R$ such that $[K_1]; G. \text{sbrf}; [K_1] = \emptyset$ | $ \{r \in K_1 \mid val(w) \in exvals(r)\}  \le 1$ <b>do</b>                                                                                                                      |

| 8:   | $K \leftarrow K_1 \cup (K_{\text{must}} \setminus codom([K_1]; G.\text{sbrf}))$   | The set of reads to be revisited                                                                                                                                                 |

| 9:   | $G' \leftarrow Remove(G, codom([K]; G. sbrf))$                                    | ▷ Remove sbrf-successors of K                                                                                                                                                    |

| 10:  | $G' \leftarrow SetRF(G', w, K)$                                                   | $\triangleright$ Make the K reads read from w                                                                                                                                    |

| 11:  | $T' \leftarrow (T \cap G'.E) \setminus dom(G'.sbrf^?; [K_1])$                     | Adjust the set of revisitable reads                                                                                                                                              |

| 12:  | Visit(G',T')                                                                      |                                                                                                                                                                                  |

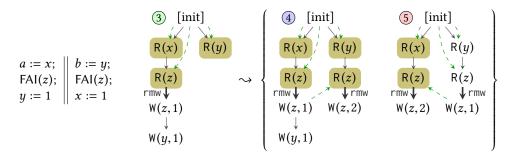

|      | $CAS(x, 1, 2) \parallel FAI(x) \parallel FAI(x)$                                  | $\begin{array}{c} [init] = \\ \hline R(x) \\ K_1 \end{array} \begin{array}{c} R(x) \\ Fmw \\ W(x, 1) \end{array} \begin{array}{c} R(x) \\ \downarrow rmw \\ W(x, 1) \end{array}$ |

Fig. 8. Example demonstrating that two revisited reads may become exclusive by REVISITREADS.

Then, intuitively, we have to consider for revisiting only subsets K that contain  $K_{\text{must}}$ . To achieve this without duplication, the process is a bit more complicated. First, at line  $_{6}$ , we remove  $K_{\text{must}}$ and all its sbrf-successors from R. Now R contains all the reads, whose revisit is entirely optional, while  $K_{\text{must}}$  contains those that must be revisited. Then, for every subset  $K_1$  of R that does not reach itself with sbrf (line 7), we take the set of reads to be revisited, K, to be the union of  $K_1$  and  $K_{\text{must}}$  (line 8). More precisely,  $K_{\text{must}}$  might be sbrf-after  $K_1$ , in which case we just take  $K = K_1$ .

Then, for each such construction of  $K_1$  and K, the actual revisit takes place. As before, we create a copy, G', of the execution containing all the events that are not sbrf-after K (line 9); change the rf-edges of *K* (line 10); adjust the revisit set (line 11); and finally explore the subexecution.

Note that line 11 adjusts the revisit set by removing reads in the sbrf-prefix of  $K_1$ , rather than of K. (Recall Fig. 4, where we the read of thread I, though revisited, is left in the revisit set in execution (2).) The reason why the sbrf-prefix of only  $K_1$  (and not also of  $K_{must}$ ) is removed from the revisit set is that revisiting  $K_1$  is optional, whereas revisiting  $K_{\text{must}}$  is forced. For every  $r \in T \cap dom(G'.sbrf^{?}; [K_1])$ , there is a loop iteration that keeps r in the revisit set and generates a graph G'' that is equal to G' when cut right after r; in particular, note that the loop iteration with  $K_1 = \emptyset$  keeps the revisit set unchanged. In contrast,  $K_{\text{must}}$  is revisited (or deleted) by all loop iterations; so if one were to remove its sbrf?-predecessors from the revisit set, one would fail to cover the executions where those reads need to be revisited.